Accumulator Shifting Unit 2

Accumulator

Main Adder

Computer Control I

Computer Control X

Computer Control II

Computer Control III

Computer Control IV

Computer Control V

Computer Control VI

Computer Control VII

Computer Control VIII

Computer Control IX

Coincidence Unit

Clock Generator

Complementer/Collater

Control Switches and Logic

Counter

Digit Pulse Generators

Engineers Control Panel

Frigs

Half Adder Type 1

Half Adder Type 2

Main Control Unit

Multiplicand Tank

Memory Units

Multiplier Tank

Order Coder

Order Decoder 1

Order Decoder 2

Order Flashing Unit

Order Tank

Printer

Sequence Control Tank

Initial Orders Loader

Timing Control Tank

Tank Address Decoder 0

Tank Address Decoder 1

Tank Address Distribution

Tank Address Flashing Units

Tank Address Decoding Final Stage

Tape Reader

Test Frigs

Transfer Unit

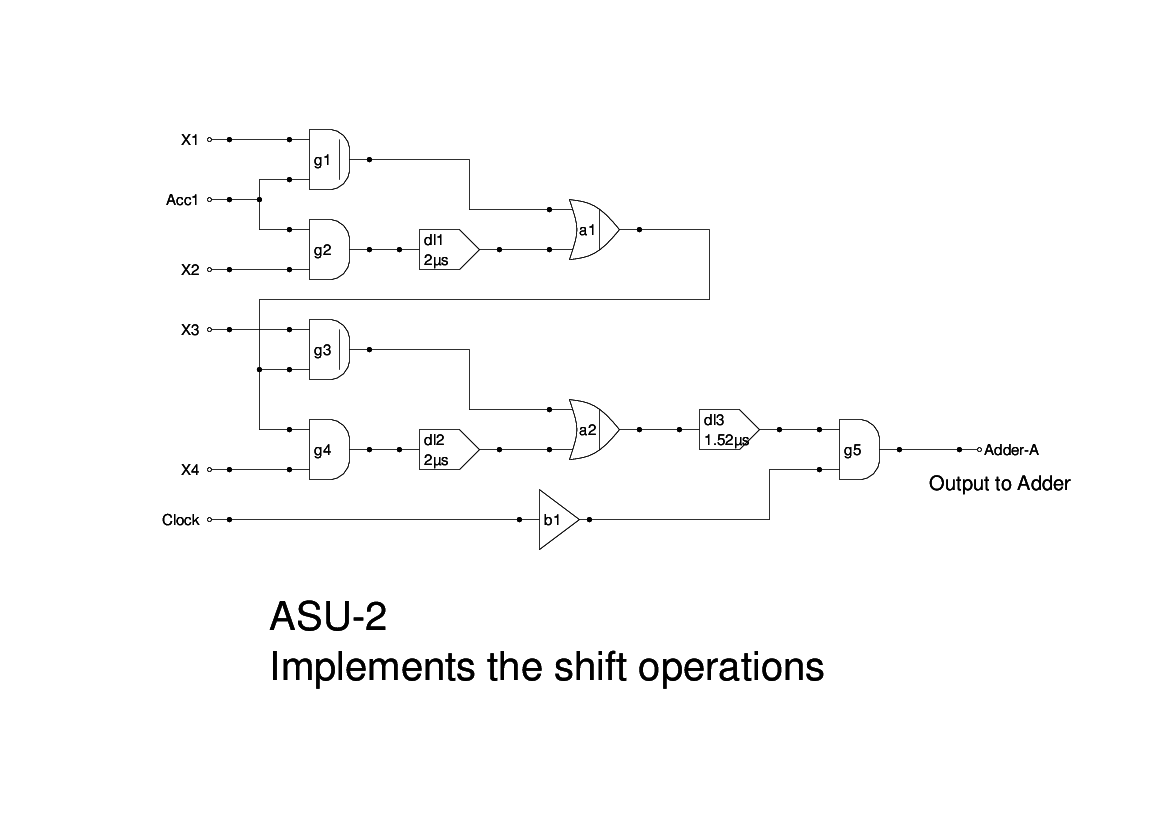

This is the Accumulator Shifting Unit. This unit normally delays the output from the Accumulator to the Adder by two pulse intervals. When a shift operation is called for, it either inserts an extra delay, or bypasses the normal delay. This causes the number to be shifted left or right according to the instruction.

In the simulation, there is an additional delay due to propagation time through the gates, and so the output is gated with a clock pulse that has been delayed by 3 timesteps. All inputs to the Adder are delayed by this amount so that the input pulses will coincide correctly.