Accumulator Shifting Unit 2

Accumulator

Main Adder

Computer Control I

Computer Control X

Computer Control II

Computer Control III

Computer Control IV

Computer Control V

Computer Control VI

Computer Control VII

Computer Control VIII

Computer Control IX

Coincidence Unit

Clock Generator

Complementer/Collater

Control Switches and Logic

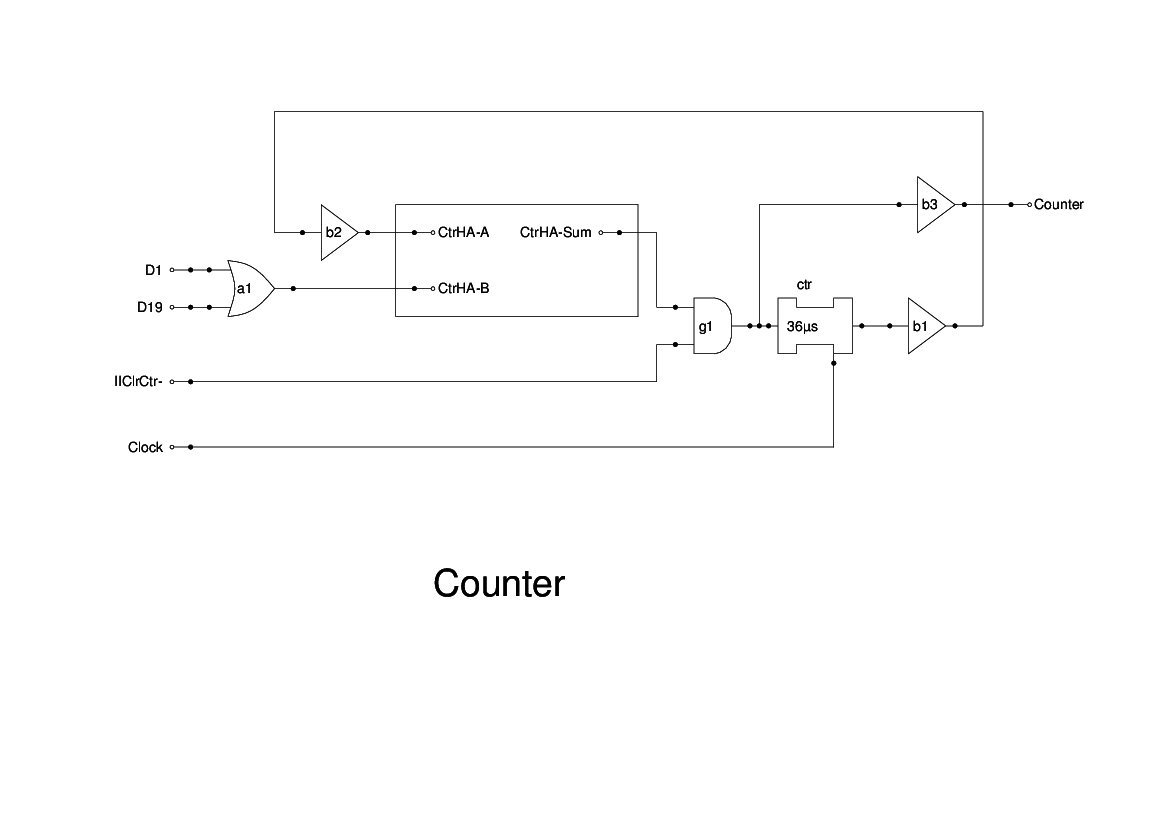

Counter

Digit Pulse Generators

Engineers Control Panel

Frigs

Half Adder Type 1

Half Adder Type 2

Main Control Unit

Multiplicand Tank

Memory Units

Multiplier Tank

Order Coder

Order Decoder 1

Order Decoder 2

Order Flashing Unit

Order Tank

Printer

Sequence Control Tank

Initial Orders Loader

Timing Control Tank

Tank Address Decoder 0

Tank Address Decoder 1

Tank Address Distribution

Tank Address Flashing Units

Tank Address Decoding Final Stage

Tape Reader

Test Frigs

Transfer Unit

The Counter is a simple half cycle delay line with a half adder. Input to the adder is provided by ORing D2 and D20. The unit therefore counts in step with the corresponding pulses in the Order Tank and Sequence Control Tank.

A slight complication was found during simulation, in that it is possible for the number to overflow and wrap around into the least significant end of the unit, and this would shift the position of all words in the memory tanks. This cannot be allowed to happen so further logic was added to suppress the most significant bits which provents this from happening. This is achieved by adding a third input to the gate g2 and arranging for this to drop for a period at the end of each cycle.

As there was only a brief textual description of this unit in the Report, I have had to devise this logic myself.